日期:2022-09-19

随着集成电路芯片向亚3纳米技术节点迈进,晶体管中关键尺寸不断微缩,带来更高的开关速度和集成度,但也会导致短沟道效应,严重影响晶体管性能,摩尔定律正逼近物理极限,这使得业界亟需开发新材料和新架构。原子级厚度的高迁移率二维半导体将取代传统硅锗,成为备选沟道材料,而栅介质的等效氧化层厚度(equivalent oxide thickness,EOT)也需微缩至0.5纳米以下。如何有效地将高迁移率二维半导体与高介电常数栅介质集成并极限微缩(EOT < 0.5纳米)是电子学领域的一个重要挑战。近日,北京大学彭海琳课题组建立了高迁移率二维半导体Bi2O2Se的紫外光辅助插层氧化方法,实现了新型自然氧化物单晶栅介质β-Bi2SeO5的可控制备,其介电常数高达22,绝缘性能优异。二维Bi2O2Se/Bi2SeO5基顶栅场效应晶体管的栅介电层EOT可微缩至0.41纳米,突破了二维电子器件超薄栅介质集成这一瓶颈。相关研究成果以“亚0.5纳米等效氧化层厚度的二维半导体单晶自然氧化物栅介质”(A single-crystalline native dielectric ftwo-dimensional semiconductors with an equivalent oxide thickness below 0.5 nm)为题,于2022年9月15日在线发表在《自然-电子学》(Nature Electronics)。

集成电路芯片中晶体管的关键尺寸在摩尔定律的推动下不断微缩。当晶体管中半导体沟道长度小于6倍特征长度(λ)时,会发生阈值电压漂移、漏电流增大等短沟道效应,制约了晶体管进一步向亚3纳米技术节点微缩。如公式λ= ![]() 所示,这一特征长度λ与晶体管的有效栅极数目(n)、半导体沟道厚度(tb)与介电常数(εb),以及栅介质的厚度(tox)与介电常数(εox)直接相关。因而,业界计划使用原子级厚度的高迁移率二维半导体材料取代传统硅锗作为沟道材料,同时需将栅介质的等效氧化层厚度(equivalent oxide thickness,EOT)微缩至0.5纳米以下,来减小特征长度λ以抑制短沟道效应。

所示,这一特征长度λ与晶体管的有效栅极数目(n)、半导体沟道厚度(tb)与介电常数(εb),以及栅介质的厚度(tox)与介电常数(εox)直接相关。因而,业界计划使用原子级厚度的高迁移率二维半导体材料取代传统硅锗作为沟道材料,同时需将栅介质的等效氧化层厚度(equivalent oxide thickness,EOT)微缩至0.5纳米以下,来减小特征长度λ以抑制短沟道效应。

然而,将高迁移率二维半导体与高介电常数的栅介质有效集成并极限微缩是电子学领域的一个重要挑战。目前,商用硅基集成电路中所用的栅介质为原子层沉积法(ALD)制备的氧化铪(HfO2),其在二维半导体无悬挂键的范德华表面难以均匀沉积,无法形成连续薄膜。而与二维半导体兼容的栅介质,如六方氮化硼(hBN)、氟化钙(CaF2)、有机缓冲层复合的HfO2等,由于介电常数较低、绝缘性不足等原因,EOT仅能微缩至0.9纳米水平。因此,二维电子学领域亟需开发与二维半导体兼容的亚0.5纳米EOT的栅介质。

北京大学化学与分子工程学院彭海琳教授课题组前期开发了新型高迁移率二维半导体Bi2O2Se(Nature Nanotechnology 2017, 12, 530),并对其氧化转化及自然氧化物介电层进行了深入研究。首次发现通过热氧化(NatureElectronics 2020, 3, 473)或等离子体氧化(Nano Letters 2020, 20, 7469),二维Bi2O2Se表面可形成具有高介电常数(21~22)和较好绝缘性能的自然氧化物栅介质Bi2SeO5(多晶或无定型相),并基于二维Bi2O2Se/Bi2SeO5构筑了高性能的场效应晶体管器件和逻辑门电路(Acc. Mater. Res. 2021, 2, 842-853),其栅介质的EOT可微缩至0.9纳米水平。

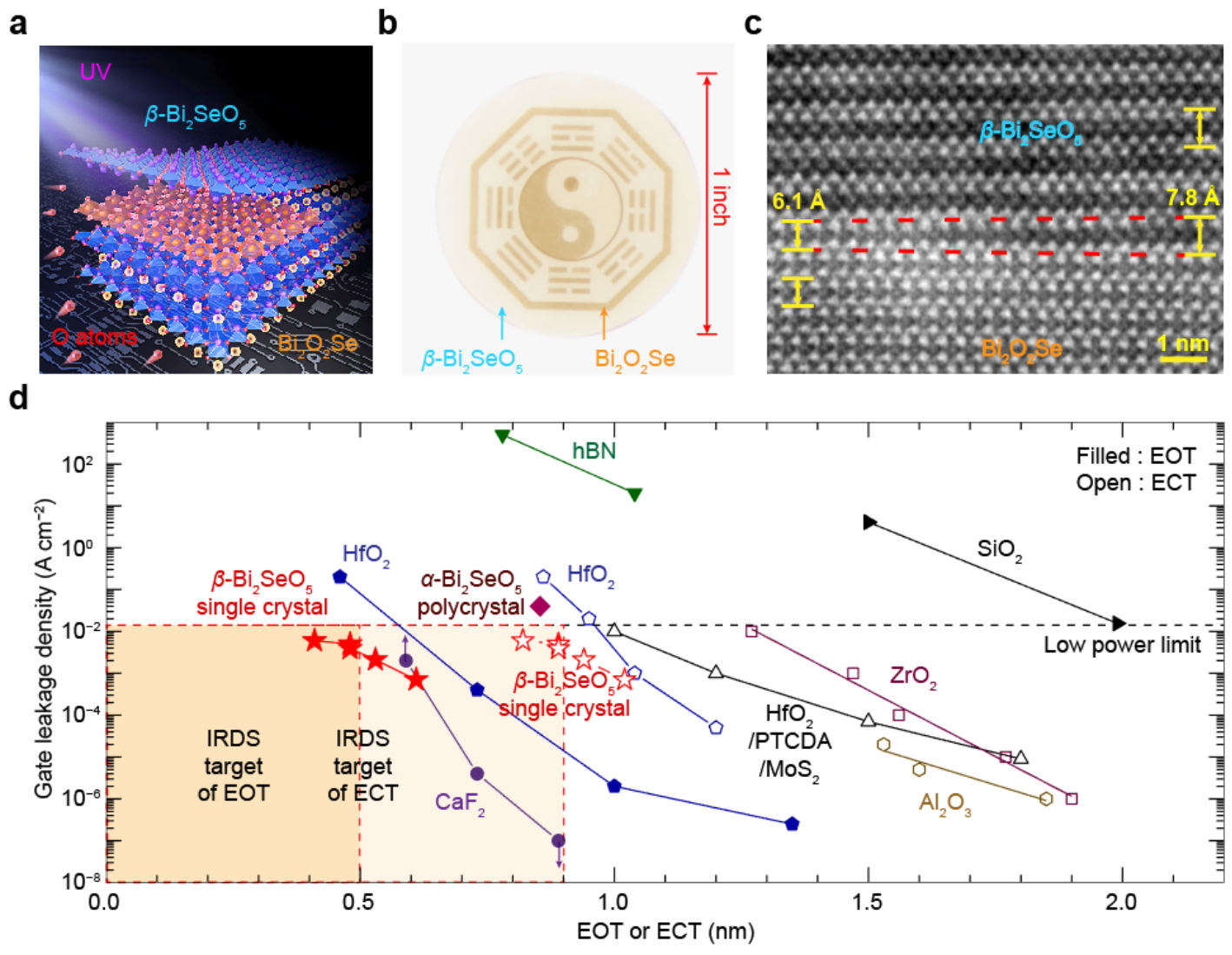

最近,彭海琳教授课题组从二维半导体Bi2O2Se的拉链形层状结构受到启发,借鉴二维材料插层化学,建立了Bi2O2Se的紫外光辅助插层氧化方法(图1a),保持其Bi-O层状骨架结构不变,将二维半导体Bi2O2Se原位转化为单晶氧化物栅介质β-Bi2SeO5。这是继先前热氧化工作制得的多晶α-Bi2SeO5介电层之后,Bi2O2Se自然氧化物的另一种物相。这种紫外光辅助插层氧化方法可与紫外光刻技术相兼容,借助特制的光刻掩模版,可实现晶圆级样品的区域选择性氧化(图1b)。二维Bi2O2Se可被逐层可控插层氧化,并形成原子级平整、晶格匹配的高质量半导体/介电层界面(图1c)。

单晶β-Bi2SeO5可用作二维Bi2O2Se基晶体管的理想栅介质。扫描微波阻抗显微镜表征和电容-电压测量表明,单晶β-Bi2SeO5具有高达22且不受厚度影响的面外介电常数。除具有高质量界面和高介电常数以外,β-Bi2SeO5栅介质还因其层状单晶结构而具有优良的绝缘性。原位插层氧化构筑的二维Bi2O2Se/Bi2SeO5顶栅场效应晶体管表现出优良的电学性能:室温迁移率可高达427 cm2/Vs,回滞可低至20~60 mV,亚阈值摆幅(SS)可低于65 mV/dec,接近理论值60 mV/dec。更重要的是,栅介质β-Bi2SeO5即使薄至3层(2.3纳米),EOT低至0.41纳米,在1 V栅压下的漏电流依然低于0.015A/cm2,满足业界低功耗器件对栅介质的要求。

单晶栅介质β-Bi2SeO5在漏电流满足业界低功耗器件要求的同时,等效氧化层厚度可以微缩到满足业界要求的亚0.5纳米水平,相对于商用HfO2、hBN、CaF2、热氧化多晶α-Bi2SeO5等各种栅介质,在等效厚度与绝缘性方面均具有优势(图1d)。该项研究成果弥补了二维半导体在超薄栅介质集成方面的短板,对二维电子器件的发展具有重要意义。

图1.单晶自然氧化物栅介质β-Bi2SeO5的制备与性质。(a)二维Bi2O2Se紫外光辅助插层氧化转化为单晶栅介质β-Bi2SeO5示意图;(b)晶圆级区域选择性制备二维Bi2O2Se / Bi2SeO5异质结;(c)二维Bi2O2Se /Bi2SeO5异质结界面结构;(d)β-Bi2SeO5的等效厚度(EOT:等效氧化层厚度;ECT:等效电容厚度)及绝缘性与其他栅介质的对比。

该研究成果于2022年9月15日在线发表在《自然-电子学》(Nature Electronics 2022, https://doi.org/10.1038/s41928-022-00824-9)。北京大学化学与分子工程学院彭海琳教授为该论文的通讯作者,第一作者为北京大学化学与分子工程学院博士研究生张亦弛。其他主要合作者还包括德州大学奥斯汀分校物理系赖柯吉教授、北京大学物理学院高鹏教授等。Nature Electronics期刊每期会挑选论文邀请作者撰写研究简介(Research Briefing),与研究论文同期在线刊出,方便读者更好地理解重要成果。彭海琳教授和张亦弛同学代表论文作者发表了题为“Producing ultrathin monocrystalline native oxide dielectrics f2D transistors(为二维晶体管制备超薄单晶自然氧化物介电层)”的研究简介,简要介绍了此项研究的背景、过程、发现和意义。

该研究工作得到了国家自然科学基金委、科技部、北京分子科学国家研究中心、腾讯基金会等机构的资助,并得到了北京大学化学与分子工程学院分子材料与纳米加工实验室(MMNL)仪器平台的支持。