来源:内容由半导体行业观察(ID:icbank) 编译自appliedmaterials ,谢谢。

日期:2022-04-23

传统的摩尔定律 2D 缩放定义了半个多世纪以来芯片行业的技术路线图。

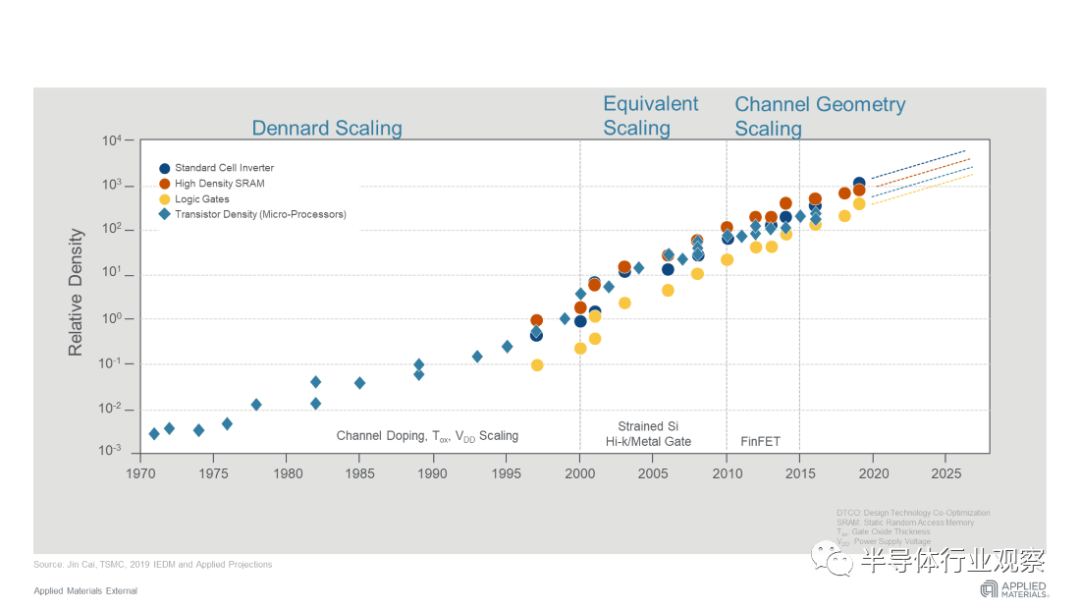

在 2000 年左右的 Dennard 缩放时代,我们每两年将晶体管尺寸减小 50%。我们缩小了控制晶体管开关状态的栅极,它的长度定义了节点:90nm、65nm等等。我们按比例缩放栅氧化层,芯片制造商在性能、功率和面积成本(或“PPAC”)方面同时获得改进。

回顾过去,进步很容易!

而在 2000 年到 2010 年间,栅极长度和栅极氧化物缩放达到了极限:我们 可以对 更小的特征进行图案化,但并非没有栅极泄漏和接触电阻等物理问题,这些问题否定了降低面积成本的性能和功率优势。我们过渡到“等效缩放”,其中栅极长度保持在 30nm 左右,物理栅极氧化物缩放停止。节点名称不再与实际尺寸相关联。相反,使用应变硅和高 K 金属栅极等材料工程技术,我们使“PP”优势继续存在,即使“AC”缩放速度减慢。

从 2010 年起,3D FinFET 架构的到来使 PP 和 AC 都取得了进一步的进展。

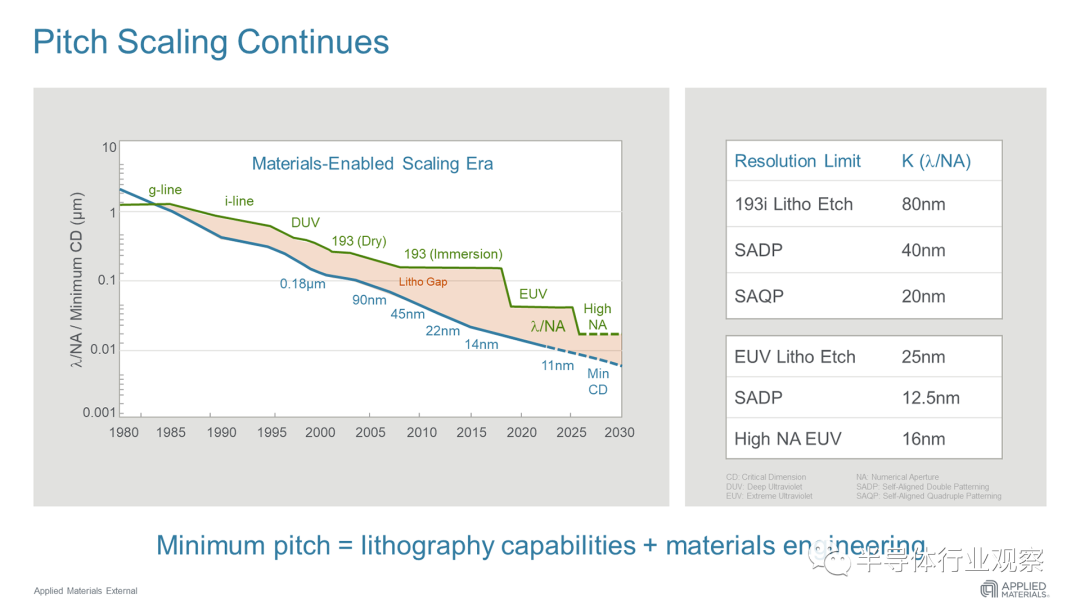

当光刻在 193nm 浸入时停滞不前时,材料工程也有所帮助——将单程图案化限制在 80nm 间距左右。双重图案化和四边形图案化分别实现了进一步缩放到 40nm 和 20nm 间距。

EUV 及时到达 5nm 节点,一步即可实现 25nm 间距图案化。然而,需要新的材料工程技术才能使 EUV 实用化。例如,在 EUV 的分辨率极限下,图案化的晶体管接触通孔很难使用传统的衬垫和填充方法填充金属:金属布线的剩余面积非常小,以至于接触电阻呈指数增长。集成材料解决方案能够选择性地沉积触点,消除衬里屏障并生产宽广的低电阻触点。

有没有进一步缩小的新方法?是的,事实上,有两个。

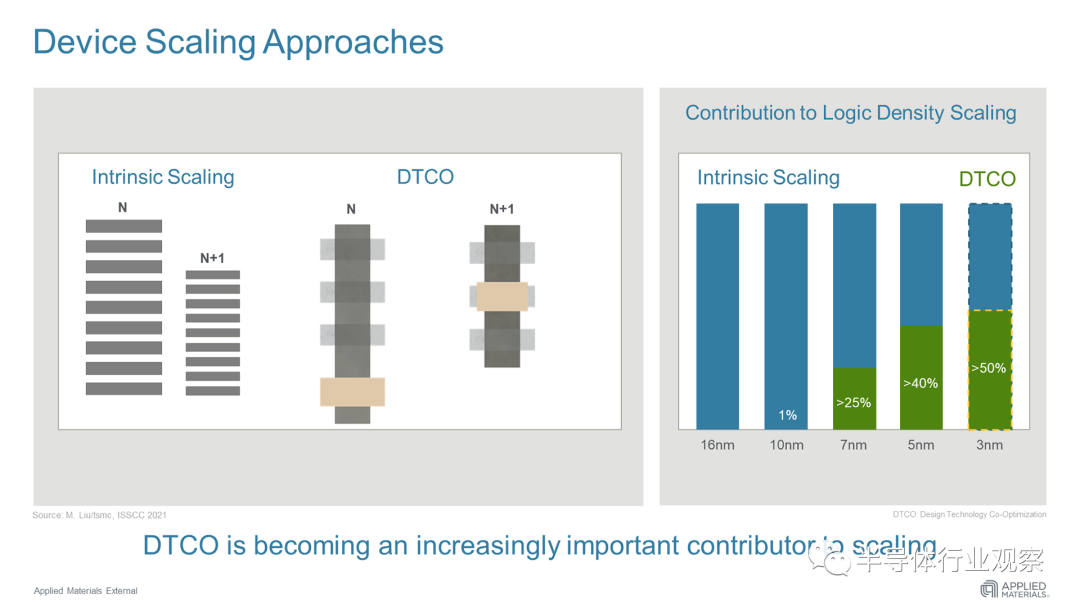

其中一个是持续的内在缩放——即经典的 2D 摩尔定律——提供了大约一半的 3nm 节点逻辑密度改进。另一个方法是来自设计技术协同优化——DTCO——指的是巧妙地重新排列逻辑单元的元件,以在恒定的光刻间距下减少单元面积。

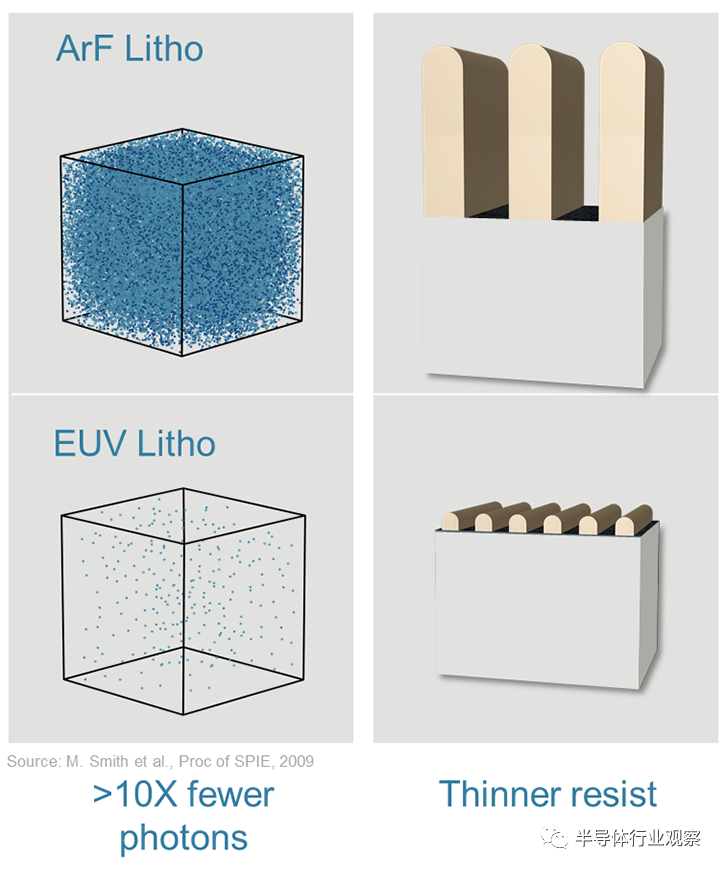

使用 EUV 技术产生光子具有挑战性且成本高昂。因此,我们需要使 EUV 光刻工作使用比DUV 少 10 倍的光子。此外,我们使用 EUV 制作的图案(例如交替的线条和空间)要窄得多。因此,EUV 光刻胶要薄得多。薄度使我们能够用更少的光子开发光掩模图案,并有助于防止狭窄的图案相互折叠。

问题 1:纠正 EUV 光刻胶中的随机误差

事实上,由于光子数和光刻胶厚度有限,我们会遇到“随机误差”,即我们在光刻胶中图案化的线条和空间中的缺陷。EUV 图案越小,随机误差在器件特征中所占的比例就越大。如果这些不规则性转移到晶圆上,它们可能会导致图案化失败——例如导致开路的线路间隙;导致短路的相邻线路之间的桥梁;芯片相邻层中的特征未对齐(称为边缘放置错误)会降低良率。

我们需要的是一种材料工程突破,可以操纵 EUV 光刻胶图案来修复随机误差并防止它们转移到晶圆上。

问题 2:降低 EUV 图案化成本

芯片设计人员已经希望制作出比 EUV 的分辨率限制更严格的图案。设计人员可以将紧密图案一分为二,这样一半的图案使用第一次 EUV 通道沉积,另一半在第二步中沉积。但是额外的 EUV 步骤会增加相当大的成本。我们需要的是一种新技术,它可以在光刻胶上轻轻地扩展 EUV 图案,从而在单次 EUV 通道后产生难以置信的紧密间距。

问题 3:提高 EUV 图案化薄膜的精度

EUV 光刻胶非常薄且细腻。因此,在蚀刻预期的图案之前,我们需要在光刻胶和晶圆之间沉积多层材料:

转移层接收来自 EUV 光掩模的图案——很快,在蚀刻完全腐蚀光刻胶之前。转移层下方是硬掩模:它接收图案并且更具弹性,可以承受在硅片中复制图案所需的更长蚀刻时间。实际上可以有不止一个硬掩模层。

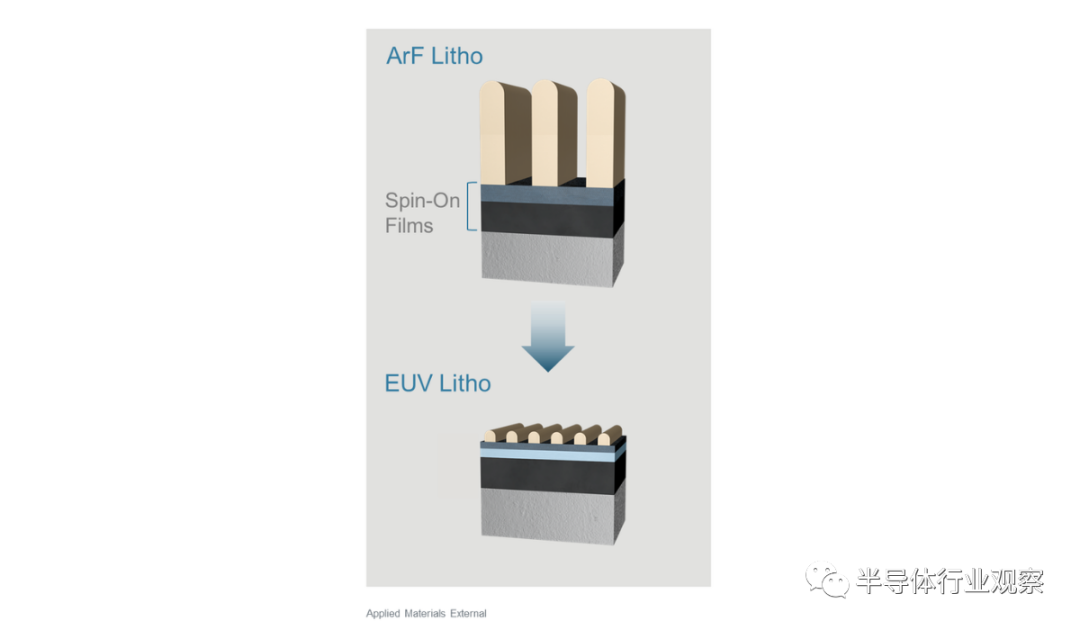

传统上,使用旋涂沉积和薄膜来形成转移层和硬掩模。薄膜以液体开始,本质上是柔软的。旋涂沉积也存在均匀性挑战。持续的 EUV 缩放需要一种新的方法。

问题 4:在我们蚀刻晶圆之前确保光刻胶图案保真度

在我们进行蚀刻之前,光学覆盖工具用于将 EUV 图案集中在晶圆上。eBeam CD SEM 工具用于补充定心,重要的是,在我们将光刻胶图案蚀刻到晶圆中之前测量它们的关键尺寸。传统的 CD SEM 电子束能量可以改变光刻胶,可能会扭曲图案。传统的 CD SEM 图像分辨率难以辨别更精细的 EUV 图案。而应用材料 eBeam 计量部门的同事正在开发一种新系统来应对这些挑战。

问题 5:解决边缘放置错误

芯片一次制作一层。每层可以包含数十亿个单独的特征,例如线、线段和通孔。这些特征中的每一个的边缘都需要与它们在上下层上的相对特征正确对齐。如果特征未对齐,则可能会出现影响功率和性能的细微错误,或者可能会破坏整个晶圆或每个晶圆上很大一部分芯片的重大错误。随着 EUV 的不断缩小,由此产生的上市时间和良率问题越来越难以解决。

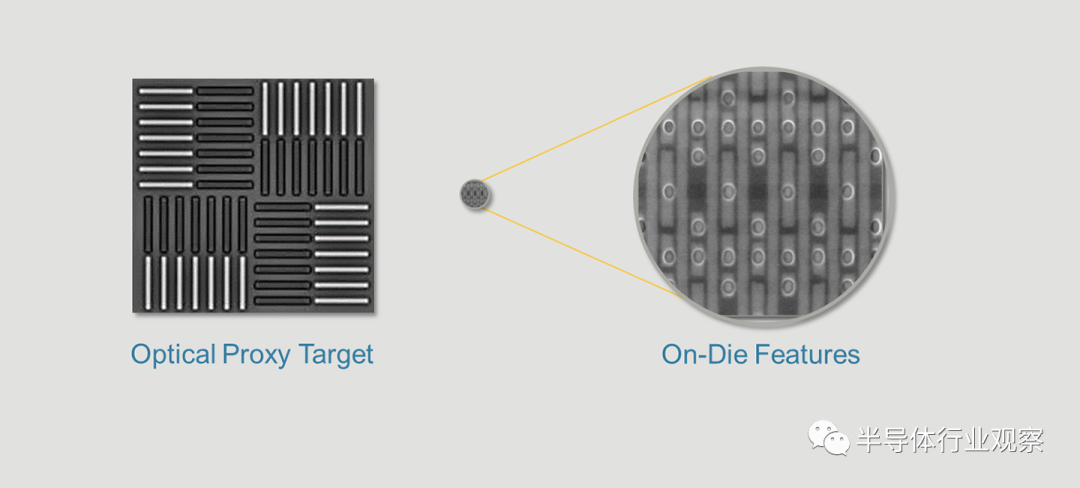

传统的光学覆盖使用放置在晶圆非活动区域中的“代理目标”来对齐各个层,例如在芯片切割过程中被锯掉的芯片之间的划线。从理论上讲,一次一层地排列这些标记,可以正确对齐芯片所有关键层上的所有数十亿个特征边缘。

在实践中,我们尝试对齐的单个特征至少比代理目标小 10 倍。此外,光刻技术中固有的细微可变性以及沉积和蚀刻等工艺步骤会产生细微的问题,例如间距步进,而这些问题无法使用光学技术看到和控制。

越来越多的光刻专家使用 eBeam 技术扫描每个 2D 层并识别图案变化。然而,他们的努力仍然主要集中在一次诊断一个 2D 层的问题上,并在扫描芯片的下一层时进行光学调整。随着我们继续使用 EUV 进行扩展,工程师们遇到了更多的“盲点”:他们尽一切可能使用光学校正,但仍然会遇到无法解决的边缘放置错误。此外,如果在大批量制造过程中出现图案偏移,依赖代理目标近似的工程师在等待新掩模时可能会损失数周的时间和产出。

行业需要的是 3D 成像和图案控制,它可以同时直接成像和测量芯片多个层的关键特征,以快速表征和诊断边缘放置错误的所有来源,包括重叠和对齐;线条和切割均匀度;线和切边粗糙度;和球场步行。

问题 6:利用大数据和人工智能加速进步

为了加快研发和大批量生产的速度,理想情况下,我们将获得大量数据并使用高级分析来解开导致图案问题的各种因素。我们将使用这些数据来创建具有最大余量的优化工艺配方——称为工艺窗口——以使 EUV 的内在缩放能够持续到未来。